2009年4月20日 星期一

Backyard garden ...

This is a broken picture due to a) high-ISO setting, and b) no stars. It will be replaced when finally the clouds is gone and instead a galaxy of stars appear in the frame of my camera.

2009年4月4日 星期六

An off-time secret mission ...

希望盡快將這個計畫處理到一個段落~ 其它 queue 起來的任務都快發霉了.

這個月多定了好幾個 HBO 頻道, 終於有時間來去轉一轉了 ...

Update: This project has been hosted here. Thanks to the help from Yihsun.

2009年3月18日 星期三

Beagleboard Specification Overview (I)

After spending some time to collect documents of all on-board devices, what is found is the exciting multimedia capability of the MPU and, especially, the IVA2.2 subsystem. IVA is the acronym of Image, Video, and Audio subsystem. It is especially amazing that the SGX module equips an universal shader engine which enables the capability to service not only the MS shader model 3 (VS and PS; GS is not mentioned in the spec so has to be invetigated in advance) and OpenGL2.0 fragment shading language (GLSL), but also, supposely, the programmable video codec engine. Universal shader engine is the trend of GPU design in 2 years ago when I'm still a Direct3D driver engineer.

Following list highlights the important features of the MPU and IVA2.2 subsystems ...1. MPU subsystem modules

- ARM subchip

Cortex-A8 core (r1p1)

ARMv7 ISA (Thumb-2, Jazelle RCT)

NEON SIMD coprocessor (VFP lite, media streaming)

16K I/D L1 cache (4 way set associative, 64 bytes cache line), 256K L2

- INTC (96 synchronous int lines)

- Asynchronous interface with core logic (this probably refers to the AXI interface)

- ICE-Crusher, ETM, ETB modules

2. IVA subsystem features (image/video/audio)

- IVA2.2, based on TMS320DMC64x+ VLIW DSP

- 32-bit fixed point

- VLIW

* 6 ALU

* 8 instructions per cycle, 8 execution units

8x8 MAC (multiply accumulate)

6x6 MAC

((a+b+c) >> 1) interpolation

two 32x32 multiply per cycle

- dynamically mixed 16/32 bit instruction sets

- 32K P(direct-mapped)/D(2-way-set 4bytes cache line) L1 cache, 48K SRAM

64K(2-way-set 128bytes cache line) L2, 32K SRAM, 16K ROM

- private DMAC

128 channel, 1D/2D addressing, 64-bit read x2 and write x2 ports, 32/64 bytes burst

- L1 INTC

- 32 entry MMU

3. PowerVR SGX

- hw 2D operations: vector graphics, BLTs, ROPs

- universal shader engine (MS VS/PS3.0, OGL 2.0)

- geometry dma

- virtualized memory addressing

- programmable video codec support: H264, H263, MPEG4, WMV9, JPEG

- 2048 x 2048 x 24bpp resolution

- 256 24-bit palette entries

- picture-in-picture(overlay), color-space conversion, rotation

- remote frame buffer support

- LCD pixel/bus interfaces (MIPI DPI/DBI 1.0)

- NTSC/PAL CVBS & S-video analog output

4. Four DMA controllers in the system

- sDMA (system DMA)

* one read and write ports

* 32 channels (prioritized)

* 96 hw-reqs

* 256 x 32 FIFO

- EDMA (enhanced DMA)

for IVA2.2 subsystem

- Display DMA

- USB HS DMA

As a novice user of a new development board, the first few things to clarify is the system power and clock distribution and the memory space mapping. Let's forget the former temporarily which is usually just a tedious spec reading, and start with the relatively "interesting" topic: the mapping of the memory space.

According to the TI application processor technical reference manual (spruf98b), the system memory space has two level of partition granularity in the 4G space:

- Level 1 - 4 quaters (Q1, Q2, Q3, Q4), each corresponds to a 1G address space

Q0 (0x00000000 ~ 0x3fffffff)

boot space (1M)

GPMC (1G)

Q1 (0x40000000 ~ 0x7fffffff)

on-chip memory (128M)

boot-rom, SRAM

L4 interconnects (128M)

L4-core (16M), L4-wakeup (256K), L4-peripherals (1M)

L4-emu (64M)

L3 interconnect (128M)

L3-control regs, SMS regs, SDRC regs, GPMC regs (16M each)

SGX (64M)

IVA2.2 (64M)

SDRC-SMS virtual address space (256M)

Q2 (0x80000000 ~ 0xbfffffff)

SDRC cs0 (512M)

SDRC cs1 (512M)

Q3 (0xc0000000 ~ 0xffffffff)

SDRC-SMS virtual address space (512M)

- Level 2 - 8 blocks, 12M each, mapped to target spaces, where target spaces includes:

* Boot Space

1M in GPMC(Q0) or (according to sys_boot5 pin configuration) ...

On-chip ROM(0x40000000~0x400fffff) space

* GPMC Space

1G Q0

8 chip selects

gpmc_ncs0 to gpmc_ncs7

16M ~ 128M each block

programmable base and size

* SDRC space

1G Q2

2 chip selects

sdrc_ncs0 and sdrc_ncs1

64M ~ 512M each block

fixed base (0x80000000), programmable size for sdrc_ncs0

programmable base (default 0xA0000000) and size for sdrc_ncs1

* VRFB / SDRC-SMS (access to SDRC space through the rotation engine)

256M Q1

512M Q3

So now we have an initial view of system bus setup and the deployment of

subsystems and devices in the memory space. Are these listed features excites

you either? Let's examine them one by one in the upcoming study plans.

2009年3月17日 星期二

2009年3月10日 星期二

Beagleboard 偷偷開箱囉 ...

偷偷放下下班後的主要任務, 跑去將一些配件收集齊全, 終於在到貨的第二天可以測一下板子是好是壞, run 的是 community 的 diagnostic process; 以下是測試概要...

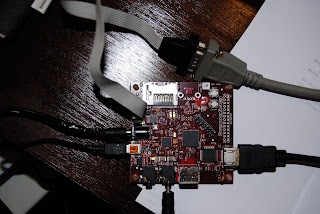

打開大大的箱子, 挖出小到幾乎像 PDA 的 PCB, 將一些配件連上後的合影:

另外蒐集的配件有 ...

- HDMI to DVI-D converter; 版子並不支援 HDMI, 只是透過 HDMI 的 connector 接上有 DVI-D interface 的 LCD monitor.

- USB A(母) to A(母); 版子上的 connector 是 mini-B, 賣場遍尋不著 mini-B to mini-B 的 cable, 所以只好用 mini-B to A(公) 的 cable, 再用這個轉接頭接上 HUB, 這樣就可以插 USB ethernet adapter 以及 USB keyboad/mouse 了;

- Externally powered USB HUB. 當 OTG port 為 host mode 時, 最多只能提供 100 mA 的電流, 因此 device 的 power 需求如果超過這個標準, 就必須由能外接電源的 HUB 來提供.

- USB ethernet adapter; 這個先備用... 因為不知道 linux 有沒它的 driver...

重點來了, 連好 null modem, 打開 terminal, 接上 5V 電源後, 第一次開機的 terminal 畫面:

bootcode 顯示在 22" LCD 的畫面 ...

照著 manual 在 SD 卡準備好 uboot 的 linux image 以及 ramdisk 之後, boot 進了熟悉的 linux command prompt, LCD 也是顯示熟悉的 framebufer driver 下的企鵝...

跑一下 default 的 video testing sample; 哇~ 好順... (相機 ISO 開到 1600, 有幾張還是晃到了)

跑一下 audio, 用的是 aplay 播 wav file...

[root@beagleboard mmc]# aplay -t wav -c 2 -r 44100 -f S16_LE -v victory-orchestral.wav

Playing WAVE 'victory-orchestral.wav' : Signed 16 bit Little Endian, Rate 44100 Hz, Stereo

Plug PCM: Hardware PCM card 0 'TWL4030' device 0 subdevice 0

Its setup is:

stream : PLAYBACK

access : RW_INTERLEAVED

format : S16_LE

subformat : STD

channels : 2

rate : 44100

exact rate : 44100 (44100/1)

msbits : 16

buffer_size : 32768

period_size : 2048

period_time : 46439

tick_time : 7812

tstamp_mode : NONE

period_step : 1

sleep_min : 0

avail_min : 2048

xfer_align : 2048

start_threshold : 32768

stop_threshold : 32768

silence_threshold: 0

silence_size : 0

boundary : 1073741824

嗯... ALSA PCM dma buffer size 32K, period size 2K, 都比我們家的 demo board 設定小很多 (256K/64K) 就能這麼順... 哈哈~ 不過這個 driver 還是有缺點啦, audio reset 的爆音超大的, 這個我們的 driver 就比她好囉... ccc~

瑕不掩瑜~

爆肝了~ let's call it a day! -_-

#over

2009年2月21日 星期六

什麼是 practical ?

當我們有一定的基礎時, 常常會害怕一切又從零開始... 現實生活中就是這種機會還蠻大的, 特別是所謂的基礎是純粹建立在好運僥倖或不公義上時; 重點是妳有沒有從零開始的能力, 當這種焠鍊臨到妳頭上時, 妳化解它的效率如何...

前朝長輩有留下東西, 這是先人辛苦奮鬥從零開始所建立起來的基礎; 後生晚輩要記住的不是這個基礎價值多少, 而應該是從零開始的經驗與技巧; 然後繼續在這個基礎上有效率地累積新資產...

開會作虛功, 就像在前人留下的資產內打轉, 沒有 energy input, 這個資產就會不斷內耗直到消逝...

2009年2月20日 星期五

跑步的話題

就像基因密碼一書提到的, 打從一出生時基因就幫妳安排好何時會有什麼疾病, 準時釋放; 但是上天的安排, 並非完全無法逆轉, 否則就沒有物競天擇這個名詞了...

小馬要求國軍體能也不無道理啦... 業務再繁重, 再多公文還沒辦, 都是欠國家的; 體能沒練好, 則是欠自己的, 這點可不能不認真!

PS. 最近發現殺彎也退步很多了... 嗯~